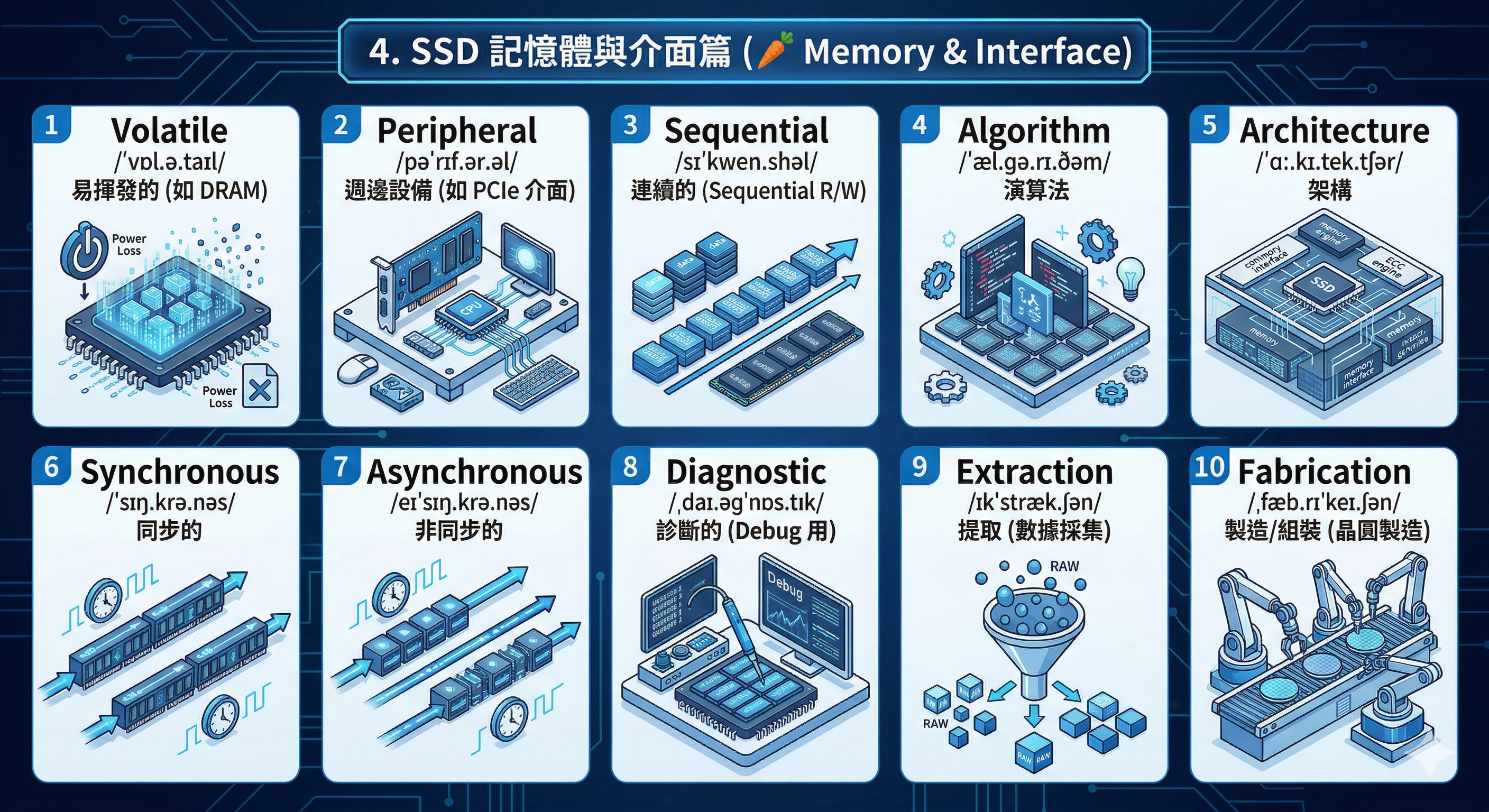

🎧 TOEIC 核心單字 — 第 4 頁:記憶體與介面篇

⬅ 第 3 頁 | 第 4 / 10 頁 | 第 5 頁 ➡

| # | 單字 | 音標 IPA | 中文 | 例句 |

review |

|---|---|---|---|---|---|

|

31

|

Volatile | adj./ˈvɒl.ə.taɪl/ |

易揮發的 (如 DRAM) |

DRAM is volatile memory — its contents are lost when power is removed. DRAM 是易失性記憶體——斷電後其內容會消失。 |

|

|

32

|

Peripheral | n./pəˈrɪf.ər.əl/ |

週邊設備 (如 PCIe 介面) |

The NVMe SSD connects through the high-speed PCIe peripheral bus. NVMe SSD 透過高速 PCIe 週邊匯流排連接。 |

|

|

33

|

Sequential | adj./sɪˈkwen.ʃəl/ |

連續的 (Sequential R/W) |

Sequential read speed is optimized for large file transfers like video editing. 連續讀取速度針對視訊編輯等大型檔案傳輸進行了優化。 |

|

|

34

|

Algorithm | n./ˈæl.ɡə.rɪ.ðəm/ |

演算法 |

The wear-leveling algorithm distributes writes evenly across all flash cells. 損耗均衡演算法將寫入操作均勻分配到所有快閃記憶體單元。 |

|

|

35

|

Architecture | n./ˈɑː.kɪ.tek.tʃər/ |

架構 |

The system architecture adopts a three-tier storage hierarchy. 系統架構採用三層儲存階層。 |

|

|

36

|

Synchronous | adj./ˈsɪŋ.krə.nəs/ |

同步的 |

Synchronous communication requires both sender and receiver to be ready simultaneously. 同步通訊要求發送方和接收方同時就緒。 |

|

|

37

|

Asynchronous | adj./eɪˈsɪŋ.krə.nəs/ |

非同步的 |

The asynchronous I/O model lets the CPU continue working while waiting for storage. 非同步 I/O 模型讓 CPU 在等待儲存設備時可以繼續運作。 |

|

|

38

|

Diagnostic | adj./ˌdaɪ.əɡˈnɒs.tɪk/ |

診斷的 (Debug 用) |

The engineer ran a diagnostic scan to identify the failing NAND block. 工程師執行診斷掃描以找出故障的 NAND 區塊。 |

|

|

39

|

Extraction | n./ɪkˈstræk.ʃən/ |

提取 (數據採集) |

Data extraction from the damaged drive took over four hours. 從損壞硬碟中提取資料花了四個多小時。 |

|

|

40

|

Fabrication | n./ˌfæb.rɪˈkeɪ.ʃən/ |

製造/組裝 (晶圓製造) |

The chip fabrication process uses a cutting-edge 5nm manufacturing node. 晶片製造流程採用先進的 5 奈米製程節點。 |

⬅ 第 3 頁 | 第 4 / 10 頁 | 第 5 頁 ➡

🧠 記憶圖 / 筆記

📝 例句練習

- DRAM is volatile memory — its contents are lost when power is removed.

DRAM 是易失性記憶體——斷電後其內容會消失。

- The NVMe SSD connects through the high-speed PCIe peripheral bus.

NVMe SSD 透過高速 PCIe 週邊匯流排連接。

- Sequential read speed is optimized for large file transfers like video editing.

連續讀取速度針對視訊編輯等大型檔案傳輸進行了優化。

- The wear-leveling algorithm distributes writes evenly across all flash cells.

損耗均衡演算法將寫入操作均勻分配到所有快閃記憶體單元。

- The system architecture adopts a three-tier storage hierarchy.

系統架構採用三層儲存階層。

- Synchronous communication requires both sender and receiver to be ready simultaneously.

同步通訊要求發送方和接收方同時就緒。

- The asynchronous I/O model lets the CPU continue working while waiting for storage.

非同步 I/O 模型讓 CPU 在等待儲存設備時可以繼續運作。

- The engineer ran a diagnostic scan to identify the failing NAND block.

工程師執行診斷掃描以找出故障的 NAND 區塊。

- Data extraction from the damaged drive took over four hours.

從損壞硬碟中提取資料花了四個多小時。

- The chip fabrication process uses a cutting-edge 5nm manufacturing node.

晶片製造流程採用先進的 5 奈米製程節點。